# Side-Channel Attacks : Sécurité et Attaques par Canaux Auxiliaires

## Tests statistiques, Attaque en Faute, Attaques de cache et micro-architecturales

---

Quentin Meunier

2025

Sorbonne Université

Laboratoire d'Informatique de Paris 6

4 Place Jussieu, 75252 Paris, France

Tests statistiques

Motivation

Généralités

Application des tests statistiques à l'évaluation des fuites

t-test spécifique et non spécifique

Attaques et tests multi-variés

Differential Fault Analysis

Attaques de cache

## Tests statistiques

Motivation

Généralités

Application des tests statistiques à l'évaluation des fuites

t-test spécifique et non spécifique

Attaques et tests multi-variés

## Differential Fault Analysis

### Attaques de cache

- Première idée : Faire plein d'attaques et s'assurer qu'elles échouent

- Suffisant ?

- Comment s'assurer qu'avec plus de traces l'attaque ne marchera pas non plus ?

- Comment s'assurer qu'il n'existe pas une attaque qu'on ne connaît pas et qui marche ?

- ⇒ Faire des attaques n'est en général pas suffisant

- Plus généralement, on souhaite pouvoir dire des choses sur la base d'observations

- **Exemple** : un nouveau médicament réduit-il vraiment la fièvre plus vite ou plus efficacement que l'ancien ?

- Les données que l'on observe varient toujours d'un patient à l'autre

- Comment savoir si la différence observée n'est pas simplement due au hasard ? (comment prendre en compte la variabilité)

- ⇒ Les observations sont souvent à la base de la prise de décision

- Statistiques : science de pouvoir dire des choses à partir d'observations

- Certains cas faciles : si on lance une pièce 20 fois et qu'on obtient 19 faces  $\Rightarrow$  Grande confiance dans le fait que la pièce est truquée

- Mais si on obtient 15 fois face ?

- **Solution** : Faire plus de lancer pour savoir

- **Problèmes** :

- Il n'est pas toujours possible d'augmenter le nombre d'observations

- Certains effets peuvent être faibles (par exemple, si la pièce fait face 51% du temps), mais on voudrait quand même s'assurer de leur absence

- Mais les statistiques permettent aussi de conclure parfois avec peu de données, même quand on pourrait croire que c'est impossible

- $\Rightarrow$  Besoin de quantification précise

- Évaluer la vraisemblance (= probabilité) des observations sous certaines hypothèses

- En déduire quelle hypothèse est la plus crédible

- À la fin, on veut une réponse oui/non, il faut donc définir **a priori** les conditions d'acceptation / de rejet, en termes de probabilité

- Approche intuitive pour l'exemple de la pièce :

- Si elle n'est pas truquée, quelle est la probabilité d'observer 15 fois face sur 20 lancers ?

- On fixe un seuil **a priori**, par exemple 5% : on conclura donc que la pièce est truquée si cette probabilité est inférieure à 5%

- $P(15 \text{ faces sur 20 lancers}) \text{ pour une pièce équilibrée} = \sum_{i=15}^{20} C_{20}^i \left(\frac{1}{2}\right)^i \times \left(\frac{1}{2}\right)^{20-i} = 2.07\%$

- On en conclut donc que les observations sont très peu compatibles avec une pièce équilibrée

- On peut toujours se tromper, mais on sait quantifier notre risque d'erreur

- On ne peut pas vraiment choisir d'autre hypothèse pour les calculs : trop de cas de pièces truquées

- $\Rightarrow$  On doit donc se contenter de la probabilité d'observation pour une pièce non truquée et conclure avec cela

- Le seuil dépend beaucoup du contexte et des conséquences associées (particule qui va plus vite que la lumière, risque d'effet secondaire grave, etc.)

- $\Rightarrow$  dépend du risque d'erreur que l'on tolère

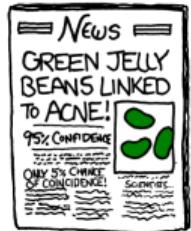

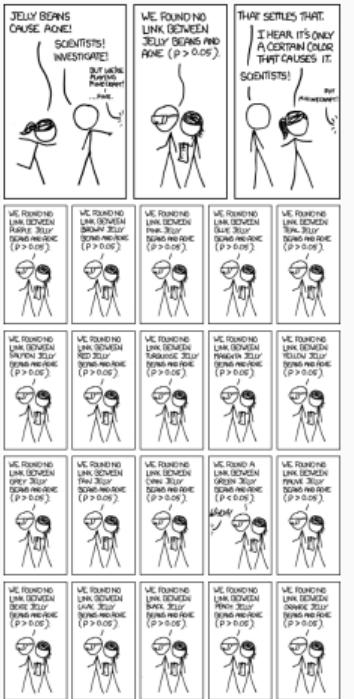

- 5% fréquent, mais : si on tolère un risque d'erreur de 5% (conclusion à tort que la pièce est truquée), cela signifie que si on fait l'expérience 20 fois pour une pièce non truquée, on se trompera en moyenne 1 fois sur les 20

## Pourquoi a-t-on besoin de statistiques ?

---

- On observe des données toujours bruitées

- Les intuitions sont parfois trompeuses

- Beaucoup de questions nécessitent de conclure même quand :

- Le nombre de données est petit

- L'effet est faible

- Les mécanismes sont complexes

- Le test statistique permet de :

- Quantifier l'incertitude

- Mesurer la plausibilité

- Prendre une décision avec un risque d'erreur maîtrisé

- **Les statistiques permettent de mettre en évidence des effets mais ne les expliquent pas**

- **But d'un test statistique** : étant donné un échantillon, on souhaite tester la vraisemblance d'une hypothèse  $H_0$  contre une autre  $H_1$

- $H_0$  est dite l'**hypothèse nulle**,  $H_1$  l'**hypothèse alternative**

- En général, on choisit  $H_1$  comme étant le complément de  $H_0$  mais ce n'est pas nécessairement le cas

- Dans le langage courant, l'hypothèse nulle est l'hypothèse qui dit qu'il n'y a pas d'effet, pas de corrélation, etc. (pas nécessairement le cas dans le test)

- Un test statistique permet de **rejeter  $H_0$**  avec un certain seuil de confiance

- Si  $H_1$  est le complément de  $H_0$ , rejeter  $H_0$ , c'est accepter  $H_1$  ; en revanche, ne pas rejeter  $H_0$  n'est pas accepter  $H_0$

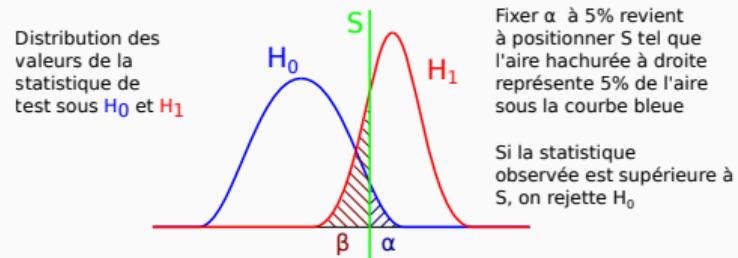

- La **statistique de test**  $S$  est une variable aléatoire définie indépendamment des données observées, qui résume l'information sur un échantillon

- On choisit  $S$  de façon à connaître sa loi sous  $H_0$

- La valeur que prend cette variable aléatoire pour les données observées est appelée **statistique observée**

- La construction d'un test donne la forme de la région de rejet de  $H_0$

- On parle de test **unilatéral** (à droite) lorsque l'on rejette  $H_0$  si la statistique observée est trop grande

- On parle de test **bilatéral** lorsque l'on rejette  $H_0$  si la statistique observée est trop grande ou trop petite

- Le risque dit de première espèce ( $\alpha$ ) est le risque de rejeter  $H_0$  à tort

- Le risque dit de deuxième espèce ( $\beta$ ) est le risque de ne pas rejeter  $H_0$  à tort

|                   |                                    | $H_0$ vraie                       | $H_0$ fausse |

|-------------------|------------------------------------|-----------------------------------|--------------|

| $H_0$ non rejetée | Bonne décision<br>( $1 - \alpha$ ) | Risque $\beta$                    |              |

| $H_0$ rejetée     | Risque $\alpha$                    | Bonne décision<br>( $1 - \beta$ ) |              |

- $\alpha$  est choisi arbitrairement, on prend typiquement  $\alpha = 0.05$  ou  $\alpha = 0.01$

- $\alpha$  et  $\beta$  sont liés : plus on diminue l'un, et plus on augmente l'autre

- La valeur limite du seuil  $\alpha$  qui conduit au rejet de  $H_0$  est appelée **p-valeur** : c'est la probabilité d'observer une réalisation de la statistique de test aussi éloignée de son espérance lorsque  $H_0$  est vraie

- En d'autres termes, c'est la probabilité d'observer quelque chose d'au moins aussi surprenant que ce que l'on observe sous l'hypothèse que  $H_0$  est vraie (on dit dès fois que c'est la probabilité que ce qu'on observe soit "dû au hasard")

- Si la **p-valeur est supérieure au  $\alpha$**  fixé, on considère qu'il n'est pas exceptionnel sous  $H_0$  d'observer la valeur effectivement observée ; par conséquent,  $H_0$  n'est pas rejetée

- Si la **p-valeur est inférieure au  $\alpha$**  fixé, la valeur observée est jugée exceptionnelle sous  $H_0$  ; on décide alors de rejeter  $H_0$

- Il existe plusieurs choses que l'on peut souhaiter tester sur un échantillon :

- L'égalité de la moyenne de l'échantillon à une valeur fixée

- La comparaison de la moyenne de l'échantillon à une valeur fixée (inférieure/supérieure)

- L'adéquation d'un échantillon à une distribution donnée

- etc.

- Chaque test statistique répond à un problème donné

- Construire un test statistique *from scratch* est difficile car à la fin il faut trouver une fonction (variable aléatoire) pour la statistique de test dont la distribution ne dépend pas des paramètres du modèle

## Problème : comment savoir si une implémentation est résistante aux SCA ?

- Point de vue du concepteur

- Différent du point de vue d'un attaquant : chercher à protéger le système de toutes les attaques

- Hypothèses différentes aussi : on connaît la clé

- **1ère approche** : tester toutes les attaques connues et vérifier que toutes échouent

- **2e approche** : caractériser les fuites secrètes de manière statistique

- Dans ce cas,  $H_0$  correspond à l'hypothèse : "il n'y a **pas de lien entre les valeurs manipulées à un instant donné et la consommation à cet instant**"

- On rejette  $H_0$  si la probabilité sous  $H_0$  d'observer ce que l'on observe est trop faible

- Ce que l'on obtient est une probabilité de fuite secrète, que l'on veut la plus petite possible

## Test de Student (ou t-test) de Welch

- Test pour comparer la moyenne de deux échantillons de tailles respectives  $n_0$  et  $n_1$  et de variances différentes

- La statistique de test est donnée par :  $t = \frac{|\bar{x}_{n_0} - \bar{x}_{n_1}|}{\sqrt{\frac{s_0^2}{n_0} + \frac{s_1^2}{n_1}}}$

- Le nombre de degrés de liberté à utiliser pour la loi de Student associée peut être approximé par :

$$v = \frac{\left( \frac{s_0^2}{n_0} + \frac{s_1^2}{n_1} \right)^2}{\frac{\left( \frac{s_0^2}{n_0} \right)^2}{n_0 - 1} + \frac{\left( \frac{s_1^2}{n_1} \right)^2}{n_1 - 1}}$$

- Avec :

- $\bar{x}_n = \frac{1}{n} \sum_{i=1}^n x_i$  la moyenne empirique d'un échantillon

- $s_n^2 = \frac{1}{n-1} \sum_{i=1}^n (x_i - \bar{x}_n)^2$  la variance empirique non biaisée d'un échantillon

- Remarque : lorsque  $n_0$  et  $n_1$  grandissent, le nombre de degrés de liberté grandit également ; dans ce cas, la loi de Student tend vers la loi normale (plus besoin de calculer  $v$ )

- Un concepteur veut savoir si son implémentation de l'AES est résistante aux SCA

- Pour cela, il fait un t-test sur chacun des bits  $i$  de l'octet de clé  $k$  en sortie de la première SBox

- Pour un bit  $i$  donné, il sépare les traces en 2 échantillons :

- Un échantillon avec les traces où le bit  $i$  vaut 0

- Un échantillon avec les traces où le bit  $i$  vaut 1

- Ici, l'hypothèse  $H_0$  est : "Les 2 échantillons ont la même moyenne", ce qui correspond à une absence de fuite

- Pour les traces où le bit  $i$  vaut 0, il obtient les mesures : 0.66, 0.54, 0.59, 0.68, 0.52, 0.61, 0.63, 0.55

- Pour les traces où le bit  $i$  vaut 1, il obtient les mesures : 0.56, 0.55, 0.58, 0.54, 0.59, 0.54, 0.57, 0.53

- On obtient  $\bar{x}_0 = 0.5975$ ,  $\bar{x}_1 = 0.5575$ ,  $s_0^2 = 0.0034$ ,  $s_1^2 = 0.00045$ ,  $t = 1.832$ ,  $v = 8.84$

## Test de Student (ou t-test) de Welch : exemple

- Pour convertir ces valeurs de  $t$  et  $v$  en probabilité, on utilise un logiciel ou on regarde dans une table

| $1 - \alpha$ | 75 %  | 80 %  | 85 %  | 90 %  | 95 %  | 97,5 % | 99 %  | 99,5 % | 99,75 % | 99,9 % | 99,95 % |

|--------------|-------|-------|-------|-------|-------|--------|-------|--------|---------|--------|---------|

| $k$          |       |       |       |       |       |        |       |        |         |        |         |

| <b>1</b>     | 1,000 | 1,376 | 1,963 | 3,078 | 6,314 | 12,71  | 31,82 | 63,66  | 127,3   | 318,3  | 636,6   |

| <b>2</b>     | 0,816 | 1,061 | 1,386 | 1,886 | 2,920 | 4,303  | 6,965 | 9,925  | 14,09   | 22,33  | 31,60   |

| <b>3</b>     | 0,765 | 0,978 | 1,250 | 1,638 | 2,353 | 3,182  | 4,541 | 5,841  | 7,453   | 10,21  | 12,92   |

| <b>4</b>     | 0,741 | 0,941 | 1,190 | 1,533 | 2,132 | 2,776  | 3,747 | 4,604  | 5,598   | 7,173  | 8,610   |

| <b>5</b>     | 0,727 | 0,920 | 1,156 | 1,476 | 2,015 | 2,571  | 3,365 | 4,032  | 4,773   | 5,893  | 6,869   |

| <b>6</b>     | 0,718 | 0,906 | 1,134 | 1,440 | 1,943 | 2,447  | 3,143 | 3,707  | 4,317   | 5,208  | 5,959   |

| <b>7</b>     | 0,711 | 0,896 | 1,119 | 1,415 | 1,895 | 2,365  | 2,998 | 3,499  | 4,029   | 4,785  | 5,408   |

| <b>8</b>     | 0,706 | 0,889 | 1,108 | 1,397 | 1,860 | 2,306  | 2,896 | 3,355  | 3,833   | 4,501  | 5,041   |

| <b>9</b>     | 0,703 | 0,883 | 1,100 | 1,383 | 1,833 | 2,262  | 2,821 | 3,250  | 3,690   | 4,297  | 4,781   |

| <b>10</b>    | 0,700 | 0,879 | 1,093 | 1,372 | 1,812 | 2,228  | 2,764 | 3,169  | 3,581   | 4,144  | 4,587   |

| <b>11</b>    | 0,697 | 0,876 | 1,088 | 1,363 | 1,796 | 2,201  | 2,718 | 3,106  | 3,497   | 4,025  | 4,437   |

| <b>12</b>    | 0,695 | 0,873 | 1,083 | 1,356 | 1,782 | 2,179  | 2,681 | 3,055  | 3,428   | 3,930  | 4,318   |

- $\alpha$  est très proche de 5% : on a environ 5% de chances de se tromper en rejetant  $H_0$ , c'est-à-dire 5% de chances de se tromper en concluant qu'il y a une fuite secrète sur ce bit

- Remarque** : Dans la pratique, le nombre de traces est souvent très grand, donc pas besoin de calculer  $v \rightarrow$  on prend la loi normale (ligne  $k = \infty$ )

- Un test est dit **spécifique** lorsque l'on cherche à caractériser la fuite sur un endroit précis d'un programme (ou circuit)

- Par exemple sur l'AES, sur le bit 0 de l'octet 0 après la première SBox

- La personne qui effectue cette caractérisation connaît le programme ou circuit, et donc la valeur de clé

- Découpage des traces en deux échantillons en fonction de la valeur du bit, calcul des moyennes et variances, puis calcul de la statistique de test

- **Problème de cette approche** : il faut tester tous les bits internes pour s'assurer qu'il n'y a pas de fuite... ( $\sim 128 \times 4 \times 10$  au minimum pour l'AES 128)

- ... mais aussi bien d'autres cas : valeur sur plusieurs bits (par exemple, valeur d'un octet à 0 vs. toutes les autres valeurs), combinaisons de valeurs intermédiaires, etc.

- Le plus commun en **multi-bit** : discriminer selon le poids de Hamming (HW), selon qu'il soit inférieur ou supérieur à 4

## t-test spécifique : exemple

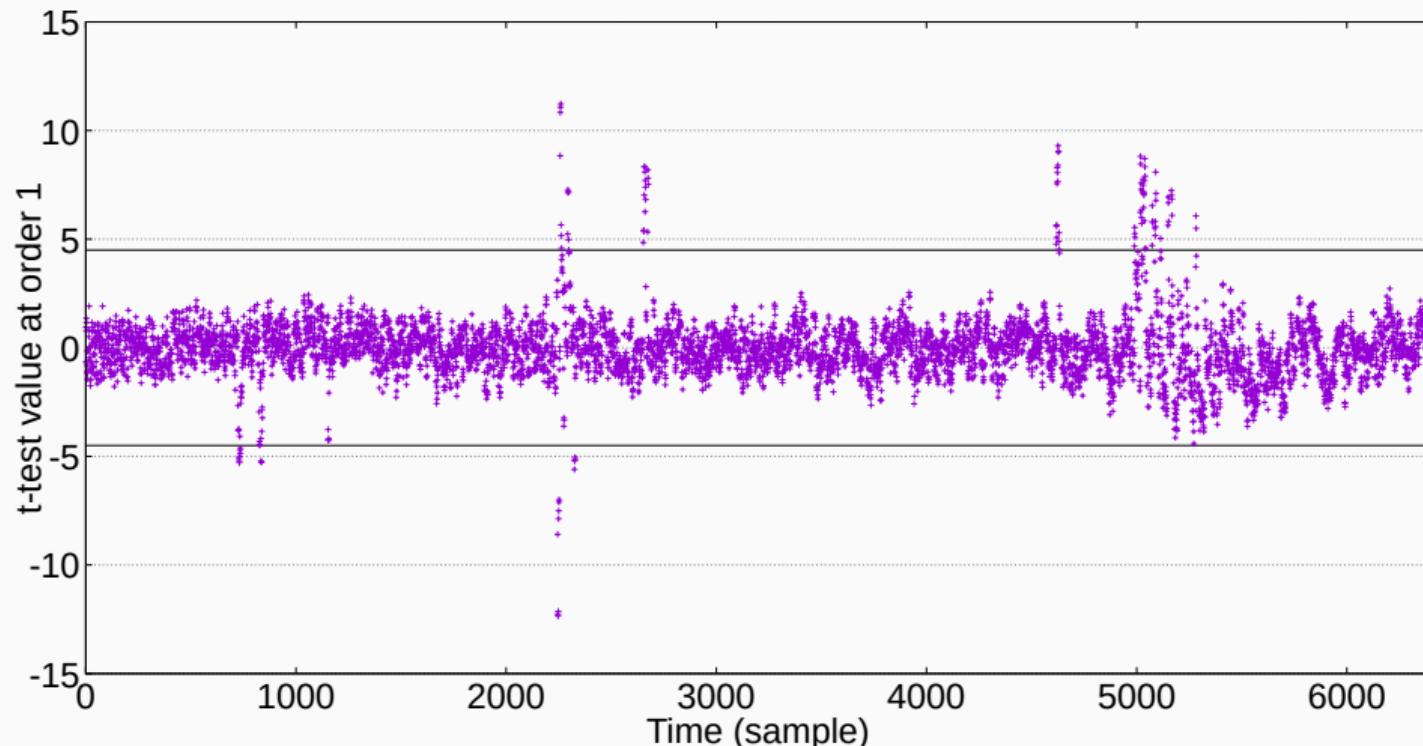

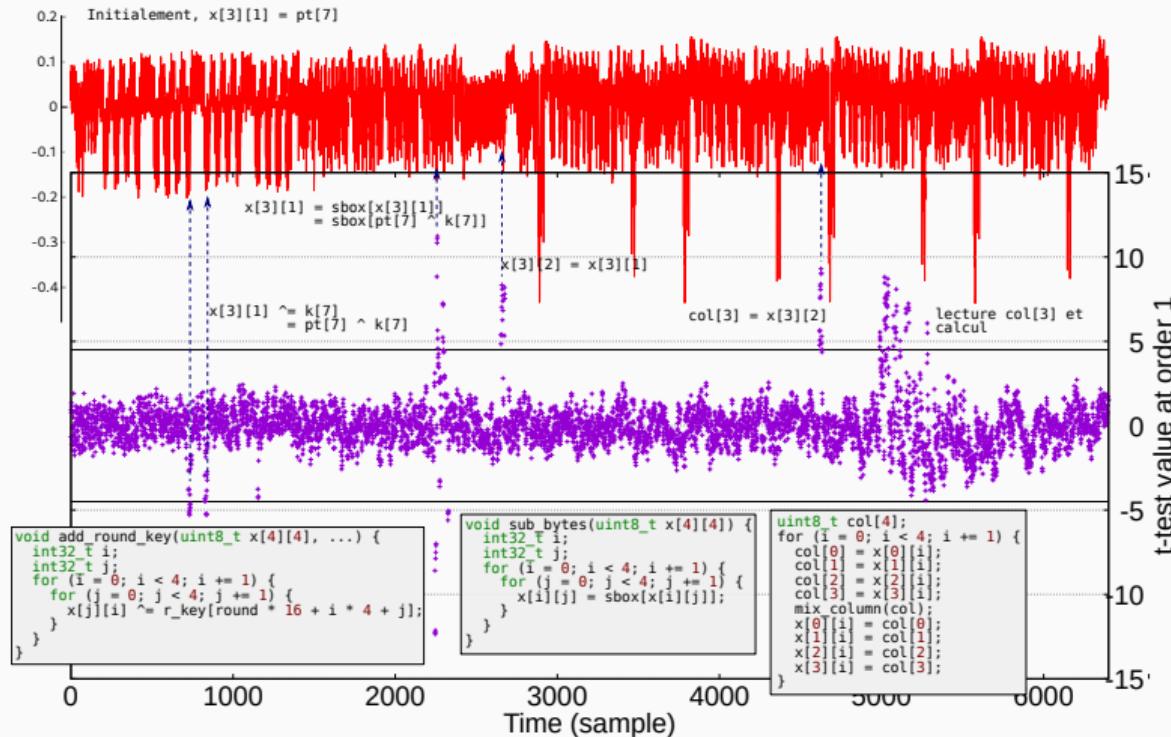

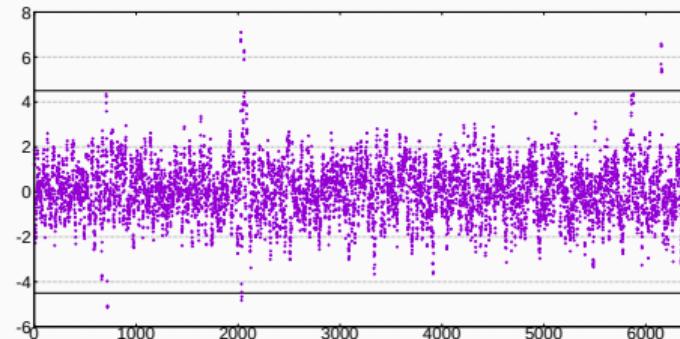

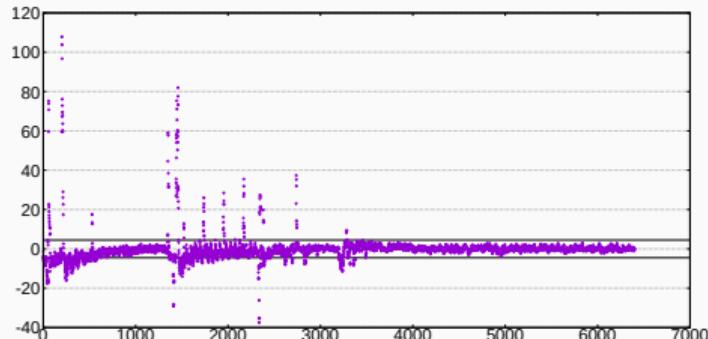

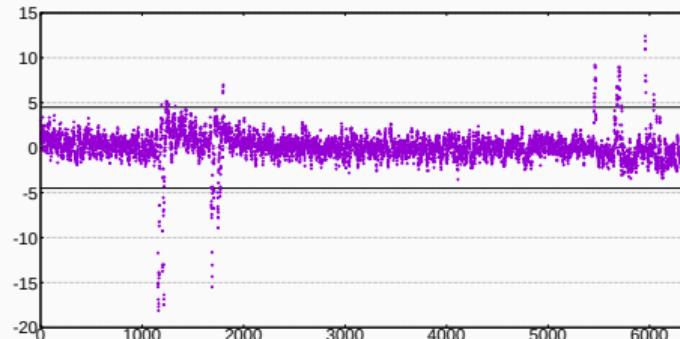

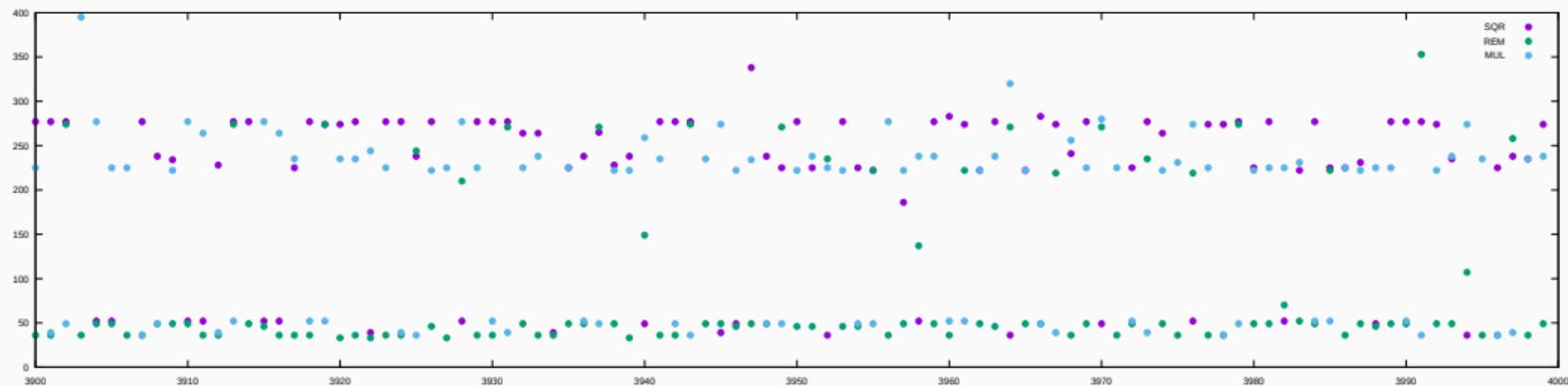

- **t-test spécifique** sur le bit 3 de l'octet [3][1] de l'état en sortie de SBox, pour la première ronde de l'AES (10 000 traces)

## t-test spécifique : exemple

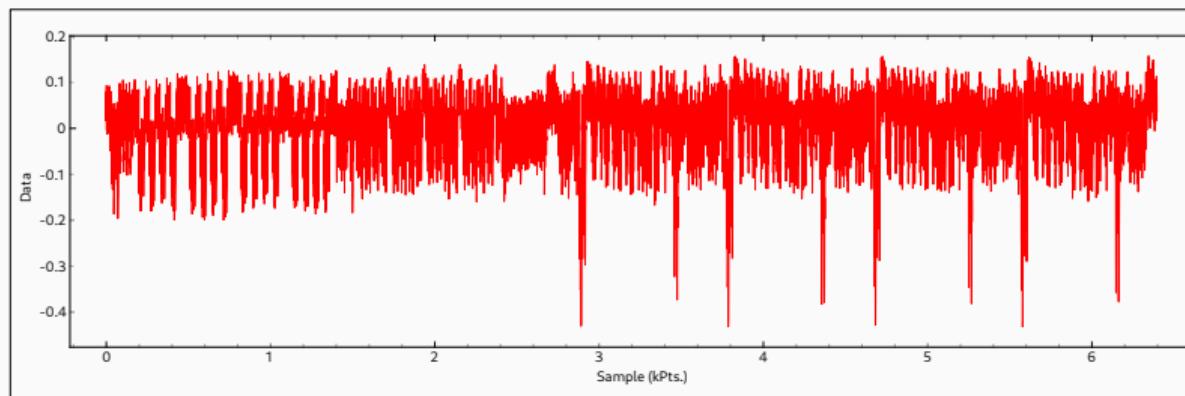

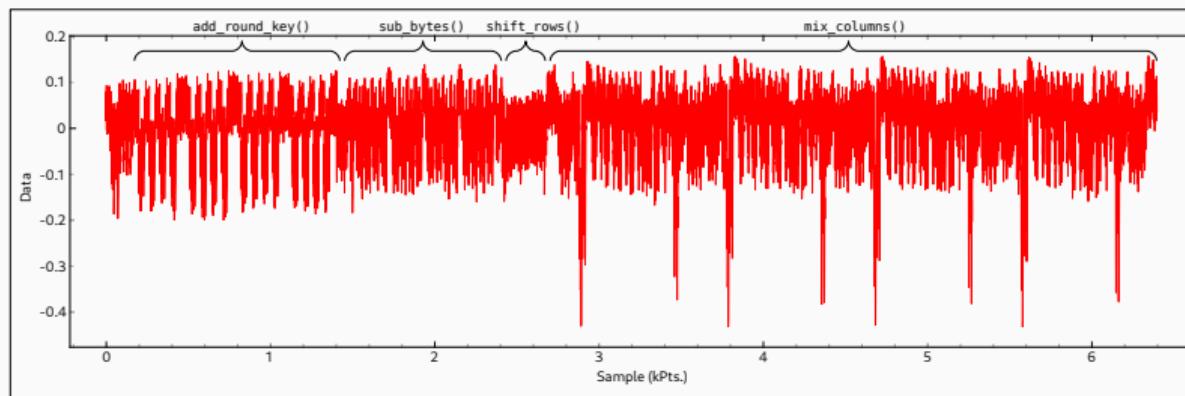

- Trace de consommation correspondante (première ronde de l'AES)

## t-test spécifique : exemple

- Trace de consommation correspondante (première ronde de l'AES)

## t-test spécifique : exemple

- t-test spécifique sur le bit 3 de l'octet [3][1] de l'état en sortie de SBox, pour la première ronde de l'AES (10 000 traces)

- Sur 8 bits, corrélation entre le HW d'une valeur et le HW de la valeur  $\oplus$  une constante cst :  $1 - 0.25 \times \text{HW}(\text{cst})$

- En théorie, les deux sont corrélés sauf quand  $\text{HW}(\text{cst}) = 4$

- En pratique, si la fuite sur la valeur est élevée, on observe une fuite quelque soit cst

- **Conséquence** : ce n'est pas parce que l'on observe une fuite sur  $\text{SBox}[\text{k} \oplus \text{pt}]$  que  $\text{SBox}[\text{k} \oplus \text{pt}]$  fuit (et donc que k fuit) : il peut s'agir uniquement d'une fuite sur pt qui "traverse" la SBox

- Corrélation entre les HW en entrée et en sortie de la SBox : 2.5%

- Corrélation entre les valeurs des bits en entrée et en sortie de la SBox :

- 9.4% pour les bits 0 et 6

- 6.3% pour les bits 1 et 4

- 4.7% pour le bit 2

- 3.1% pour le bit 7

- 0 pour les bits 3 et 5

- $\Rightarrow$  Pose la question du **modèle de fuite** : valeurs lues/écrites en mémoire ? Lues/écrites en registres ?  $\oplus$  de l'ancienne et de la nouvelle valeur lors de l'écriture en registre ?

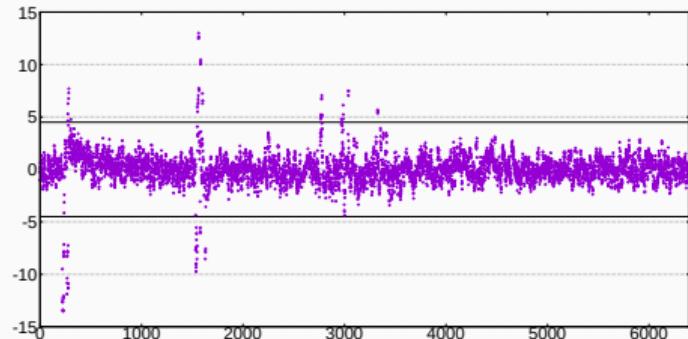

## t-test spécifique : autres exemples

IV :  $\text{HW}(\text{SBox}[\text{pt}0 \wedge \text{k}0])$

IV :  $\text{SBox}[\text{pt}6 \wedge \text{k}6] \wedge 0x4$

IV :  $\text{HW}(\text{pt}15)$

IV :  $\text{HW}(\text{SBox}[\text{pt}12 \wedge \text{k}12])$

- **Grande variabilité** en fonction du bit, de l'octet et de la valeur ciblée

- Effets bizarres

- Fuites sur `pt[15]` à chaque itération externe de `sub_bytes`

- Valeurs à la fin de `mix_columns`

- Fuite plus grande avant la SBox alors que la valeur ciblée est après

- Certaines observations ne peuvent pas être expliquées sans connaître le détail du processeur

- **Remarque** : pour  $N = 10000$ , p-valeurs pour des valeurs de la statistique :

- 4.5 → 0.000008

- 6 → 0.000000005

- 8 → 0.000000000000001

- 9 → 0 avec la précision maximale dans R (22 chiffres après la virgule)

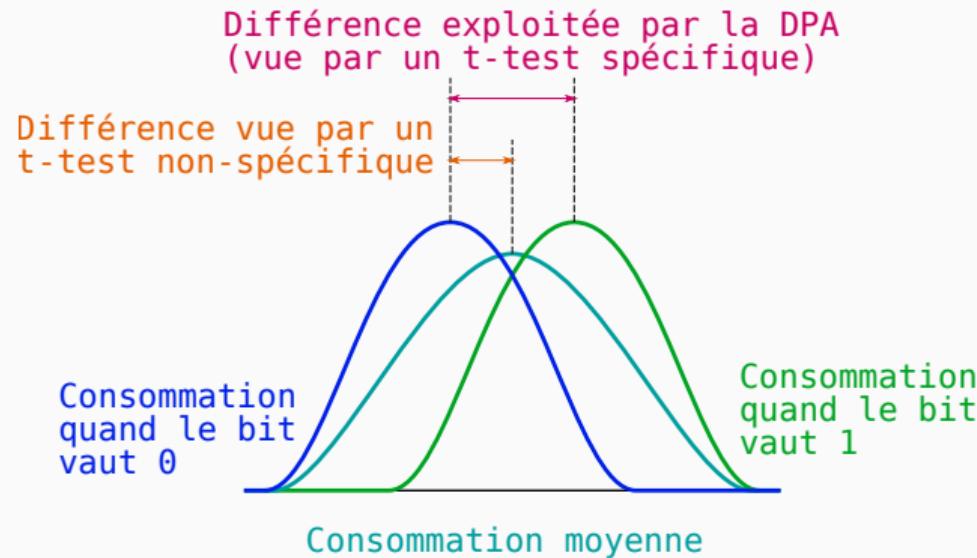

## t-test non-spécifique

- Cherche à répondre au problème de l'infaisabilité en pratique de tous les t-test spécifiques

- **Idée** : si un bit interne fuit de l'information (consommation) selon sa valeur 0 ou 1, alors la moyenne entre 2 ensembles de traces, dont l'un correspond à une valeur du bit fixe et l'autre à une valeur aléatoire (uniforme), doit avoir un écart observable

- Soit un **bit intermédiaire du calcul  $w$** , et à l'instant de son calcul, les moyennes de consommation  $\mu_{w=0}$  et  $\mu_{w=1}$  des traces pour lesquelles il vaut respectivement 0 et 1

- Si ces moyennes sont suffisamment différentes (i.e. que  $w$  **fuit de l'information**), alors elles sont chacunes éloignées de la moyenne de toutes les traces  $\mu \simeq \frac{\mu_{w=0} + \mu_{w=1}}{2}$  (si  $n_0 \simeq n_1$ )

- Il suffit donc de tester le programme avec des **entrées fixées** d'un côté *vs.* des **entrées aléatoires** de l'autre et de regarder pour chaque instant si on observe un écart de moyenne entre les deux ensembles de traces associés

- La statistique de test au moment du calcul de  $w$  sur un test non-spécifique est forcément plus petite que celle sur un test spécifique sur la valeur de  $w$  si  $w$  fuit de l'information, puisque  $\mu_{w=0} < \mu < \mu_{w=1}$  ou  $\mu_{w=1} < \mu < \mu_{w=0}$

- Pour les variances, on doit avoir  $s^2 > s_{w=1}^2$  et  $s^2 > s_{w=0}^2$  donc le dénominateur de la statistique de test est plus grand pour un test non-spécifique

- $\Rightarrow$  Ces 2 effets font que le test non spécifique est **moins sensible**

- Une fuite détectée sur un t-test non spécifique  $\Rightarrow$  une fuite détectée un t-test spécifique

- Mais le t-test non spécifique ne dit pas de quel bit il s'agit...

- En pratique, on peut avoir un algorithme avec des variables secrètes, publiques, et des masques

- Qu'est-ce qui est fixe en *fixed* et qu'est-ce qui varie en *random* ?

- Les masques devraient toujours varier (en *fixed* et *random*)

- Cas 1 : (PT random, K fixe) vs. (PT random, K random)

- Cas 2 : (PT fixe, K fixe) vs. (PT random, K random)

- Cas 3 : (PT fixe, K fixe) vs. (PT random, K fixe)

- Cas 4 : (PT fixe, K fixe) vs. (PT fixe, K random)

- Problème cas 1 : le PT peut ici agir comme un masque, or dans le pire cas il pourrait être constant

- Problème cas 2 : détecte les fuites sur le plaintext et la clé, pas uniquement la clé

- Problème cas 3 : détecte les fuites sur le plaintext

- ⇒ Le cas 4 devrait être utilisé de préférence quand c'est possible (clé variable), sinon cas 3 :

- Équivalent dans certains cas, dans l'AES par exemple car on commence par xorer clé et plaintext

- Mais ne permet pas de capturer les fuites sur le Key Schedule : pour capturer les fuites sur les bits de la clé, il faut que la clé varie en *random*

- **Ne pas faire** :  $x_1 + x_2 + \dots + x_n$  puis diviser par  $n$

- **Raison** : quand le nombre de termes à sommer est grand, différence progressive entre les ordres de grandeurs des termes sommés

- **Faire** :  $\bar{x}_0 = 0$ , puis itérativement :  $\bar{x}_i = \bar{x}_{i-1} + \frac{x_i - \bar{x}_{i-1}}{i}$

- $\Rightarrow$  La même idée peut être appliquée au calcul de la variance pour n'avoir qu'une passe sur les données

### Avantages de n'avoir qu'une passe sur les données

- Permet de calculer régulièrement la statistique de test (par exemple toutes les 1000 traces) et de s'arrêter dès que le seuil est dépassé : évite de regarder toutes les traces si une fuite apparaît dès 1000 traces

- Quand le nombre de traces est très élevé, permet de calculer la statistique sans avoir à stocker les traces

- Jusqu'à présent, nous n'avons considéré que la fuite **en un point** (univarié)

- Une attaque **multi-variée** cherche à mettre en relation des mesures de différents instants

- Il faut savoir quels instants on veut mettre en relation : sinon, explosion combinatoire

- Exemple en bi-varié pour 3000 samples : 9 millions de combinaisons possibles

- Le but est de choisir des instants où les mesures devraient être **corrélées**, et où leur combinaison permet de révéler de l'information

- Utile pour **attaquer les codes masqués** : si l'on ne considère qu'un seul instant, il n'y a pas de fuite d'information

- Par exemple, une CPA bi-variée (dite à l'ordre 2) permet de retrouver la clé d'un code masqué à l'ordre 1

- De la même manière, il y a des tests statistiques multi-variés

- Dans le schéma présenté, en sortie de SBox à la première ronde, expressions du type  $SBox[k \oplus pt] \oplus m'$

- $\Rightarrow$  **Plus de fuite** selon le modèle de fuite en valeur

- Supposons que l'on ait accès à la consommation de l'expression  $m'$

- Comment **combiner** les consommations aux deux instants pour annuler  $m'$  ?

- On ne peut pas faire un “ $\oplus$ ” sur les consommations

- **Idée** : il faut trouver un moyen de corréler une fonction des consommations avec le  $\oplus$  des deux valeurs

- Sous l'hypothèse que la consommation est le HW, il faut donc trouver une fonction  $f(HW(SBox[k \oplus pt] \oplus m'))$ ,  $HW(m')$  qui ait une corrélation non nulle avec  $HW((SBox[k \oplus pt] \oplus m') \oplus m') = HW(SBox[k \oplus pt])$

- **Fonction possible** : valeur absolue de la différence

- En effet sur 8 bits, si  $u$  et  $v$  sont uniformes et indépendants :

$\rho(|HW(u) - HW(v)|, HW(u \oplus v)) = 0.24$

- Sous l'hypothèse que la consommation est le HW,  $|HW(u) - HW(v)| = |P(u) - P(v)|$

- $\Rightarrow$  On cherche donc à maximiser la corrélation entre  $|P(SBox[k \oplus pt] \oplus m') - P(m')|$  et  $HW(SBox[k \oplus pt])$

- Si impossible d'obtenir la consommation correspondant à l'expression  $m'$ , possible de faire l'attaque **sur 2 expressions masquées** :  $HW(SBox[k0 \oplus pt0] \oplus m')$  et  $HW(SBox[k1 \oplus pt1] \oplus m')$

- **Inconvénient** : requiert de tester 65 536 hypothèses de clé au lieu de 256

- Mais en réalité, on en revient à **l'architecture et au code assembleur**

- Même registre pour  $m'$  et  $SBox[k \oplus pt] \oplus m'$  :

fuite en transition de  $SBox[k \oplus pt]$

- $\Rightarrow$  CPA à l'ordre 1

- Sinon, si la SBox est calculée dans une boucle, **même registre** utilisé pour toutes les expressions SBox

- Au moment de la première transition :

fuite de  $HW(SBox[k0 \oplus pt0] \oplus SBox[k4 \oplus pt4])$

- $\Rightarrow$  CPA à l'ordre 1 possible avec 65 536 hypothèses

Tests statistiques

Differential Fault Analysis

Attaques de cache

Tests statistiques

Differential Fault Analysis

Attaques de cache

- **Retrouver un secret** à partir d'une faute lors de l'exécution d'un algorithme de chiffrement

- L'effet de la faute doit en général être assez précis par rapport :

- Au moment où elle intervient durant l'exécution

- À la donnée modifiée et sa taille (bit, mot)

- En général, on n'obtient pas directement la clé recherchée, mais une réduction de l'espace d'états (valeurs possibles pour la clé)

- L'attaquant se base sur la valeur du ciphertext fauté, en la comparant avec le ciphertext non fauté par une analyse différentielle

- **Hypothèse** : pouvoir générer plusieurs chiffrements avec le même plaintext

- **Glitch d'horloge** : front montant qui arrive plus tôt que prévu

- **Glitch de tension** : surtension pendant un très court instant

- **Impulsion électromagnétique** proche du circuit

- **Laser** : impulsion laser sur le circuit décapsulé

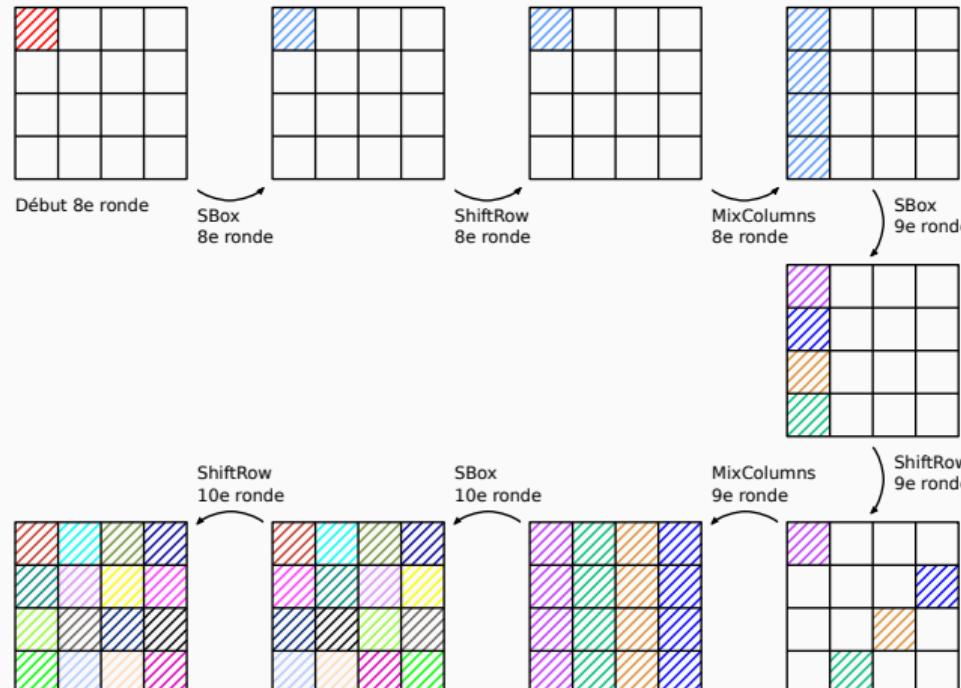

## Exemple de DFA : “single-fault” sur l’AES

- **Hypothèse** : la faute se produit au début de la 8e ronde et affecte un octet du *state* (n’importe comment mais un seul octet)

- Cas du premier octet avec une faute  $\delta$  :  $x' = x \oplus \delta$

# Exemple de DFA : “single-fault” AES

Texte chiffré avec faute

|     |     |     |     |     |     |     |     |     |     |      |      |      |      |      |      |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|

| x'0 | x'1 | x'2 | x'3 | x'4 | x'5 | x'6 | x'7 | x'8 | x'9 | x'10 | x'11 | x'12 | x'13 | x'14 | x'15 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|

2e AddRoundKey

10e ronde

|     |     |      |      |

|-----|-----|------|------|

| x'0 | x'4 | x'8  | x'12 |

| x'1 | x'5 | x'9  | x'13 |

| x'2 | x'6 | x'10 | x'14 |

| x'3 | x'7 | x'11 | x'15 |

ShiftRow

10e ronde

AddRoundKey<sup>1</sup>

10e ronde

ShiftRow<sup>1</sup>

10e ronde

SBox

10e ronde

SBox<sup>-1</sup>

10e ronde

1er AddRoundKey

10e ronde

Après MixColumns

9e ronde

MixColumns

9e ronde

|    |    |    |    |

|----|----|----|----|

| d1 |    |    |    |

|    |    |    | d4 |

|    |    | d3 |    |

|    | d2 |    |    |

Après ShiftRow

9e ronde

SBox<sup>-1</sup>[x'0+k0]

|    |    |     |     |

|----|----|-----|-----|

| x0 | x4 | x8  | x12 |

| x1 | x5 | x9  | x13 |

| x2 | x6 | x10 | x14 |

| x3 | x7 | x11 | x15 |

2e AddRoundKey

10e ronde

ShiftRow

10e ronde

SBox

10e ronde

SBox<sup>-1</sup>[x'0+k0]

AddRoundKey<sup>1</sup>

10e ronde

ShiftRow<sup>1</sup>

10e ronde

SBox<sup>-1</sup>

10e ronde

|    |    |    |    |    |    |    |    |    |    |     |     |     |     |     |     |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|

| x0 | x1 | x2 | x3 | x4 | x5 | x6 | x7 | x8 | x9 | x10 | x11 | x12 | x13 | x14 | x15 |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|

Texte chiffré Sans faute

On en tire donc les 4 équations suivantes

- $2\delta = SBox^{-1}[x_0 \oplus k_0] \oplus Sbox^{-1}[x'_0 \oplus k_0]$

- $\delta = SBox^{-1}[x_{13} \oplus k_{13}] \oplus Sbox^{-1}[x'_{13} \oplus k_{13}]$

- $\delta = SBox^{-1}[x_{10} \oplus k_{10}] \oplus Sbox^{-1}[x'_{10} \oplus k_{10}]$

- $3\delta = SBox^{-1}[x_7 \oplus k_7] \oplus Sbox^{-1}[x'_7 \oplus k_7]$

- $\delta, k_0, k_{13}, k_{10}$  et  $k_7$  sont des inconnues, les  $x_i$  et  $x'_i$  sont connus

- **Résolution** : pour chaque valeur de  $\delta$ , on énumère pour chaque équation les valeurs possibles de  $k_i$ .

- Chaque équation retourne **0, 2 ou 4** valeurs possibles pour  $k_i$

- Si aucune des 4 équations ne retourne 0 valeur possible pour  $k_i$ , alors cette valeur de  $\delta$  est possible, et la combinaison des  $k_i$  **doit être explorée**

- Il y a (toujours ?) 15 valeurs de  $\delta$  satisfaisant les 4 équations, presque toujours 2 valeurs possibles pour les  $k_i$  dans ce cas, soit 240 ou 256 combinaisons à explorer pour 4 octets de clé

- En répétant le processus avec les équations pour les autres colonnes, il y a moins de  $2^{32}$  valeurs possibles pour la clé entière

- Nécessite un *key schedule* inverse puis un chiffrement complet pour chaque hypothèse de clé complète

- ⇒ On peut faire une énumération exhaustive (~30 minutes sur ma machine pour un code séquentiel compilé en -O3)

- Pour considérer une faute sur les autres octets de  $x$  au début de la 8<sup>e</sup> ronde, on peut calculer les équations correspondantes

- Il n'y a en réalité que 4 ensembles de 16 équations car chaque ensemble de 16 équations est valide pour 4 octets différents

- On peut retrouver la clé en environ 2h (code séquentiel sur une machine moyenne) pour une faute sur n’importe quel octet de  $x$

Tests statistiques

Differential Fault Analysis

Attaques de cache

Tests statistiques

Differential Fault Analysis

Attaques de cache

- Attaques plutôt récentes

- Concernent un grand nombre de processeurs

- Atténuation des effets de ces attaques pas facile

- Peuvent être utilisées en combinaison d'autres attaques (ex : Meltdown)

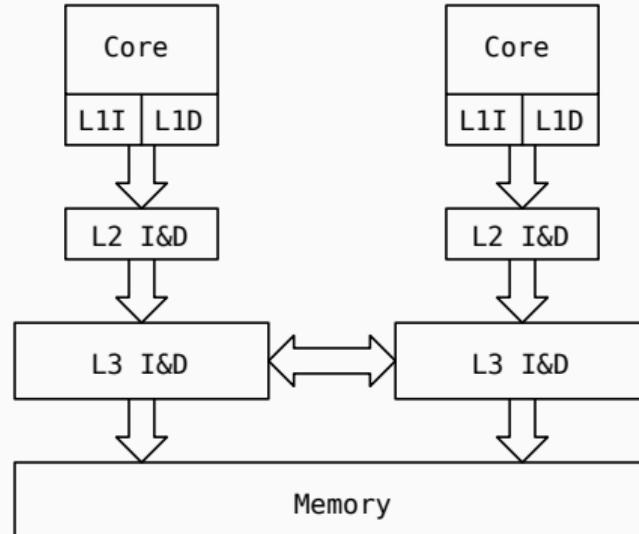

# Hiérarchie mémoire des processeurs Intel

- Le cache L3 est **partagé** entre les coeurs

- Les données incluses dans les caches L1/L2 sont forcément dans le cache L3 : **caches inclusifs**

- Comment utiliser cela pour faire une attaque ?

- **Question** : puisque les pages physiques des processus sont disjointes (mécanisme de mémoire virtuelle), quel intérêt ?

- Bibliothèques dynamiques

- *Memory deduplication* (ou *Kernel Same-page Merging*) : technique utilisée dans les hyperviseurs de machines virtuelles (mais aussi dans les OS) pour réduire l'empreinte mémoire

- ⇒ Il y a donc des pages partagées (en lecture) entre les processus

- **1<sup>ere</sup> Remarque** : si on invalide (*flush*) une ligne de cache du L3, elle est invalidée dans tous les caches L1/L2 (conséquence de la propriété d'inclusivité)

- ⇒ On peut donc s'amuser à ralentir les autres processus

- Mais ça ne fait pas une attaque...

- **2<sup>e</sup> Remarque** : un hit en cache est plus rapide qu'un miss

- Et donc...

- ...Si un autre processus exécute du code d'une librairie partagée, on peut savoir **si des instructions** contenue dans une ligne de cache **ont été exécutées**

- **Principe :**

```

1     flush(line with some insts);

2     wait();

3     a = timestamp();

4     load(line with some insts)

5     b = timestamp()

6     line_acessed = (b - a) < threshold

```

- OK, mais je n'ai rien à cacher...

- ...Si un autre processus exécute du code d'une librairie partagée, on peut savoir **si des instructions** contenue dans une ligne de cache **ont été exécutées**

- **Principe :**

```

1     flush(line with some insts);

2     wait();

3     a = timestamp();

4     load(line with some insts)

5     b = timestamp()

6     line_acessed = (b - a) < threshold

```

- OK, mais je n'ai rien à cacher...

- ...Sauf quand j'utilise RSA !

- Algorithme de chiffrement **asymétrique** avec paire (clé publique, clé privée) pour l'envoi de messages chiffrés à un destinataire identifié et la signature de messages

- Utilisé pour l'échange de clé des algorithmes symétriques en général

- Étapes pour la génération des clés :

- Choisir  $p, q$  deux nombres entiers **premiers** et calculer  $n = pq$

- Choisir un **exposant public**  $e$  (par exemple  $e = 65537$ )

- Calculer l'**exposant privé**  $d = e^{-1} \bmod (p-1)(q-1)$

- La clé privée est  $(p, q, d)$

- La clé publique est  $(n, e)$

- **Chiffrement** (ou vérification de signature) :  $E(m) = m^e \bmod n$

- **Déchiffrement** (ou signature) :  $D(c) = c^d \bmod n$

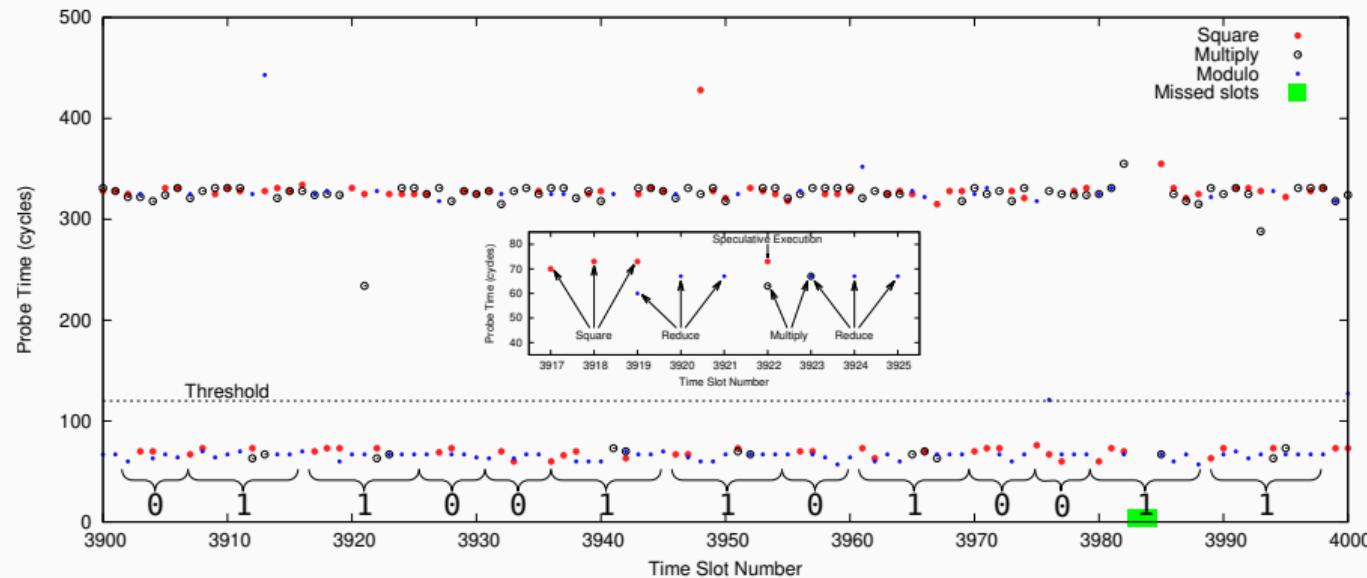

## Pseudo-code de l'exponentiation modulaire

```

1  mpi_t exp(mpi_t b, mpi_t e, mpi_t m) {

2      mpi_t res = 1;

3      for (int32_t i = 64; i >= 0; i -= 1) {

4          res = square(res);

5          res = modulo(res, m);

6          if (get_bit(e, i) == 1) {

7              res = mult(res, b);

8              res = modulo(res, m);

9          }

10     }

11     return res;

12 }

```

- Connaitre la séquence des fonctions appelées parmi `square`, `modulo` et `mult` permet de retrouver l'exposant

- Bien sûr, ce code se trouve dans une librairie dynamique

- Et donc un autre processus que celui qui fait le déchiffrement peut **retrouver l'exposant secret  $d$**

- En réalité, ce n'est pas aussi immédiat pour CRT-RSA, mais retrouver l'exposant lors du déchiffrement permet quand même de retrouver la clé secrète

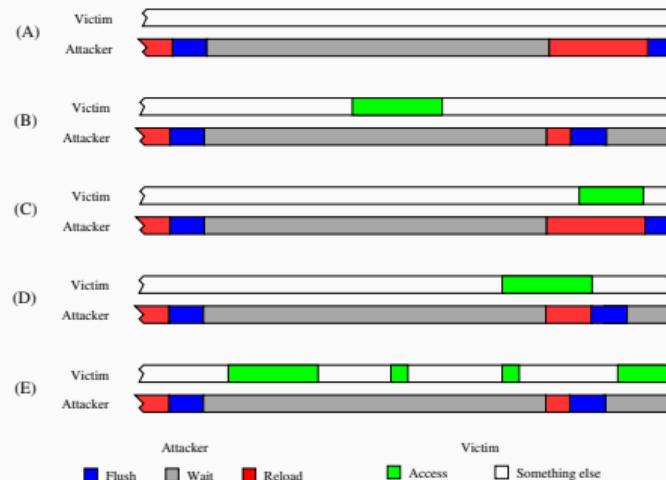

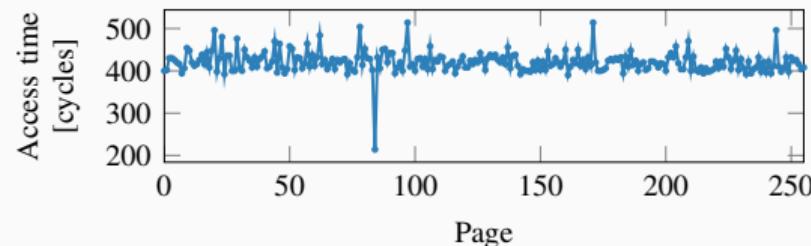

# Principe de l'attaque Flush+Reload [Yarom and Falkner, 2014]

- Scénarios (source image : [Yarom and Falkner, 2014]) :

- A : Pas d'accès du processus victime

- B : Accès du processus victime

- C : Accès du processus victime durant le reload (manqué)

- D : Reload durant l'accès du processus victime (potentiellement manqué)

- E : Multiples accès du processus victime

## Flush+Reload sur l'exponentiation de RSA

(source image : [Yarom and Falkner, 2014])

- **Difficulté** : compromis pour trouver la bonne durée d'attente

- Trop courte : plus grande chance de manquer des accès à cause de recouvrements

- Trop longue : détection d'un seul accès au lieu de plusieurs

- **Configuration préalable** : détermination du seuil qui discrimine un hit d'un miss sur la machine

- Code d'autres applications tournant en même temps sur la machine

- Interruptions

- Préfetch des lignes de cache

- ⇒ Éviter les débuts de fonction

- Compliqué à faire soi-même ?

## Flush+Reload en pratique : Sources d'erreur

- Code d'autres applications tournant en même temps sur la machine

- Interruptions

- Préfetch des lignes de cache

- ⇒ Éviter les débuts de fonction

- Compliqué à faire soi-même ?

## Flush+Reload en pratique : Sources d'erreur

- Code d'autres applications tournant en même temps sur la machine

- Interruptions

- Préfetch des lignes de cache

- ⇒ Éviter les débuts de fonction

- Compliqué à faire soi-même ?

- Que des 1 ?

- Extrait du code dans la fonction d'exponentiation de la lib MPI (Multi-Precision Integer)

```

_gcry_mpih_sqr_n (xp, rp, rsize, tspace);

}

xsize = 2 * rsize;

if ( xsize > msize )

{

_gcry_mpih_divrem(xp + msize, 0, xp, xsize, mp, msize);

xsize = msize;

}

tp = rp; rp = xp; xp = tp;

rsize = xsize;

/* To mitigate the Yarom/Falkner flush+reload cache

* side-channel attack on the RSA secret exponent, we do

* the multiplication regardless of the value of the

* high-bit of E. But to avoid this performance penalty

* we do it only if the exponent has been stored in secure

* memory and we can thus assume it is a secret exponent. */

if (esec || (mpi_limb_signed_t)e < 0)

{

/*mpih_mul( xp, rp, rsize, bp, bsize );*/

if( bsize < KARATSUBA_THRESHOLD )

_gcry_mpih_mul ( xp, rp, rsize, bp, bsize );

else

_gcry_mpih_mul_karatsuba_case (xp, rp, rsize, bp, bsize,

&karactx);

xsize = rsize + bsize;

if ( xsize > msize )

{

_gcry_mpih_divrem(xp + msize, 0, xp, xsize, mp, msize);

xsize = msize;

}

}

```

- Si les caches L3 ne sont pas partagés par les différents coeurs : **Flush+Flush** [Gruss et al., 2016]

- La durée de l'instruction flush diffère selon que la ligne se trouve ou non dans la hiérarchie mémoire

- Comme Flush+Reload, mais flush au lieu du reload

- Pas d'accès mémoire requis, marche aussi quand les caches sont partagés

- Pas d'accès à une instruction comme rdtsc pour mesurer le temps

- Utiliser des API comme `clock()`, `clock_gettime()` (la précision peut ne pas être assez importante)

- En dernier recours, utiliser un thread qui incrémente un compteur volatile

- Si l'architecture ne contient pas d'instruction flush (ou si celle-ci est privilégiée) : **Evict+Reload** [Gruss et al., 2015]

- ⇒ Remplir les sets du cache correspondant à la ligne à espionner en faisant plein d'accès à des lignes mappées dans ce set

- Peut nécessiter de faire du rétro-engineering sur la politique de remplacement du cache

- Avantage : les pages n'ont plus besoin d'être partagées entre les processus

- Variante : **Prime+Probe** [Osvik et al., 2006]

- Remplir tous les ways des sets à observer

- Attendre

- Déterminer quels sets sont toujours occupés

- Ces attaques ont une moins bonne précision et une moins bonne granularité que Flush+Reload

## Utilisation des attaques de cache pour faire une Covert Channel

---

- **Covert channel** : canal de communication (caché) entre deux processus dont le système n'a pas connaissance : permet de casser l'isolation des processus (un processus peut fuiter des informations sans en avoir les droits)

- Les deux processus peuvent s'envoyer des messages en faisant des lectures en cache à des adresses prédéfinies

- Un processus fait une lecture à une adresse correspondant à 0 et 1 (ou de 0 à 255), puis l'autre processus regarde quelle ligne fait hit et en déduit le caractère transmis

# Covert Channel en pratique

```

\subfigure[Sémantique de la primitive CAS-2 en pseudo-code]{

\begin{minipage}[t]{0.57\linewidth}

\begin{code}(\textbf{if} T == \textbf{addr1}, T \textbf{old1}, T \textbf{old2}, T \textbf{new1}, T \textbf{new2}){}

\textbf{hsspace*}{0.5cm}\textbf{code}{atomic}{}\\

\textbf{hsspace*}{0.5cm}\textbf{code}{\textbf{if}(*addr1 == old1 \& & *addr2 == old2 ){}\\

\textbf{hsspace*}{1cm}\textbf{code}{addr1 = new1;}\\

\textbf{hsspace*}{1cm}\textbf{code}{addr2 = new2;}\\

\textbf{hsspace*}{1cm}\textbf{code}{\textbf{return} true;}\\

\textbf{hsspace*}{0.5cm}\textbf{code}{\textbf{else}}{}\\

\textbf{hsspace*}{1cm}\textbf{code}{\textbf{return} false;}\\

\textbf{hsspace*}{0.5cm}\textbf{code}{\textbf{return}}{}\\

\textbf{hsspace*}{0.5cm}\textbf{code}{\textbf{end atomic}}{}\\

\textbf{code}{}}\\

\label{fig:semantique_cas2}

\end{minipage} \hfill

\caption{Sémantique des primitives CAS et CAS-2 en pseudo-code}

\label{fig:semantique_cas2}

\end{figure}}

```

Principalement deux types d'améliorations existent pour cette instruction : la meilleure consiste à pouvoir opérer un CAS sur un nombre de cases du CCAS- $n$  pour  $n = 25$  est illustrée figure-\ref{fig:semantique\_cas2}. Cette instruction est couramment nommée CAS-2 ou DDCAS (possible, consiste à pouvoir effectuer des CAS sur des mots de plus grande taille ; ces instructions peuvent être vues comme des CAS- $n$  avec  $n$  être contigus. Si l'instruction CAAS opérait sur 2 mots est relativement répandue dans les jeux d'instructions des processeurs, l'instruction CCAS- $n$  pour  $n > 25$  n'existe pas dans aucune architecture comme étant directement implantée en matériel.

Malheureusement pour ce modèle de programmation, la primitive CAS seules, même opérant sur deux mots, reste légère pour beaucoup d'ailleurs nécessaire pour que ce modèle de programmation puisse avoir un nombre plus élevé d'implémentations de structures de données efficaces. Il aurait fallu que cette modélisation de programmation ne soit pas si difficile à utiliser.

## \subsection{Le modèle de programmation transactionnel}

Une autre alternative aux verrous est le modèle de programmation transactionnel, introduit en 1977 par Lomet-\cite{conf/lrds/Lomet77}. Les instructions réalisées de manière atomique du point de vue des autres tâches s'exécutant de manière concurrente. Cela offre une abstraction, puisqu'un programmeur peut ainsi raisonner sur la correction de son code à l'intérieur d'une transaction sans se soucier des interactions.

Issue du domaine des bases de données, la sémantique des transactions mène à quatre propriétés, connues sous le nom de "propriétés ACID".

Le modèle de programmation transactionnel restreint la notion de transaction à deux seules : atomicité et isolation. Le programme résultant de l'exécution du code contenu dans une transaction est indissociable du point de vue des autres threads. En d'autres termes, un autre thread ne peut observer que l'état immédiatement avant ou immédiatement après la transaction. Il garantit que les tâches exécutant de manière concurrente ne peuvent pas affecter le résultat d'une transaction allant à son terme. Ainsi, une transaction doit produire le même résultat que si aucune autre tâche ne s'exécutait en même temps.

- Il faut ajouter de la **redondance** et des mécanismes de **correction d'erreur** + gérer le descheduling/rescheduling des threads

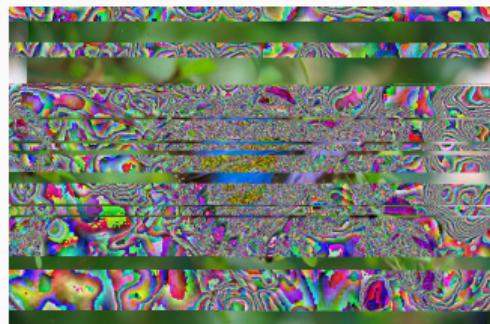

- Peut alors être très robuste : implémentation du protocole SSH sur des caches entre 2 machines virtuelles allouées sur des serveurs amazon [Maurice et al., 2017]

(a) Image distortion caused by insertion and deletion errors due to scheduling.

(b) Noisy image after handling insertion and deletion errors.

(c) The image after applying error correction. It is equivalent to the original image.

(Source [Maurice et al., 2017])

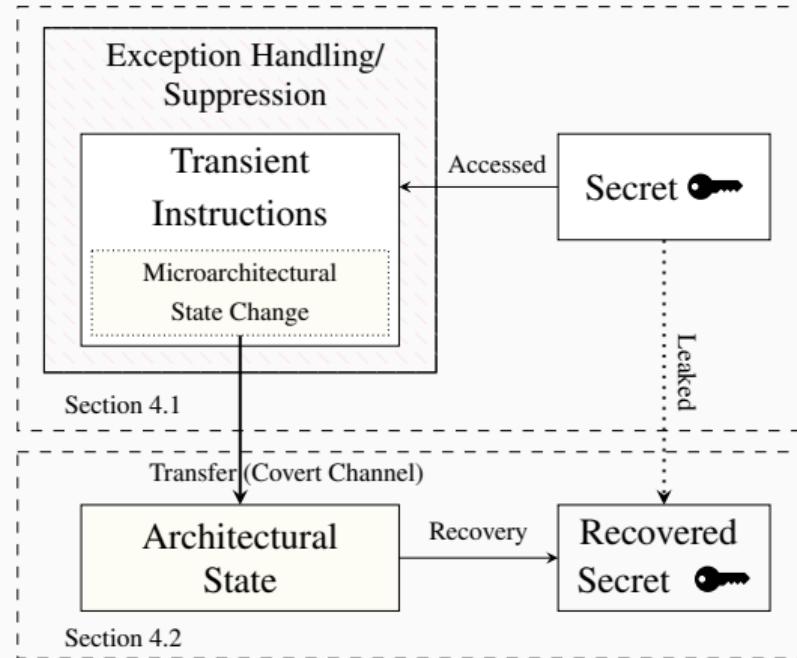

- Bug rendu public le 3 Janvier 2018

- Affecte tous les processeurs Intel du marché

- Permet de lire la mémoire de tous les processus tournant sur une machine

- Attaque dite **micro-architecturale** : combine une attaque de cache avec une attaque sur l'exécution out-of-order

- Source de toutes les images : [Lipp et al., 2018]

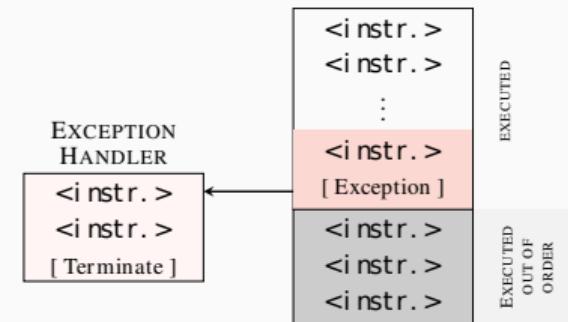

- Mécanisme matériel pour augmenter la performance d'un processeur

- Une instruction assembleur donnée peut s'exécuter avant une autre instruction assembleur qui la précède dans le code source

- Souvent combiné à de l'exécution spéculative, i.e. sans savoir si l'instruction exécutée sera vraiment exécutée, suite à un branchement

- En cas d'exécution spéculative à tort ou d'exception : tous les registres sont réinitialisés à une valeur correcte ou par défaut

## Meltdown : Combiner l'exécution out-of-order avec Flush+Reload

- Possible de voir l'effet d'une instruction jamais exécutée

```

1 raise_exception();

2 // the line below is never reached

3 access(probe_array[ data * 4096]);

```

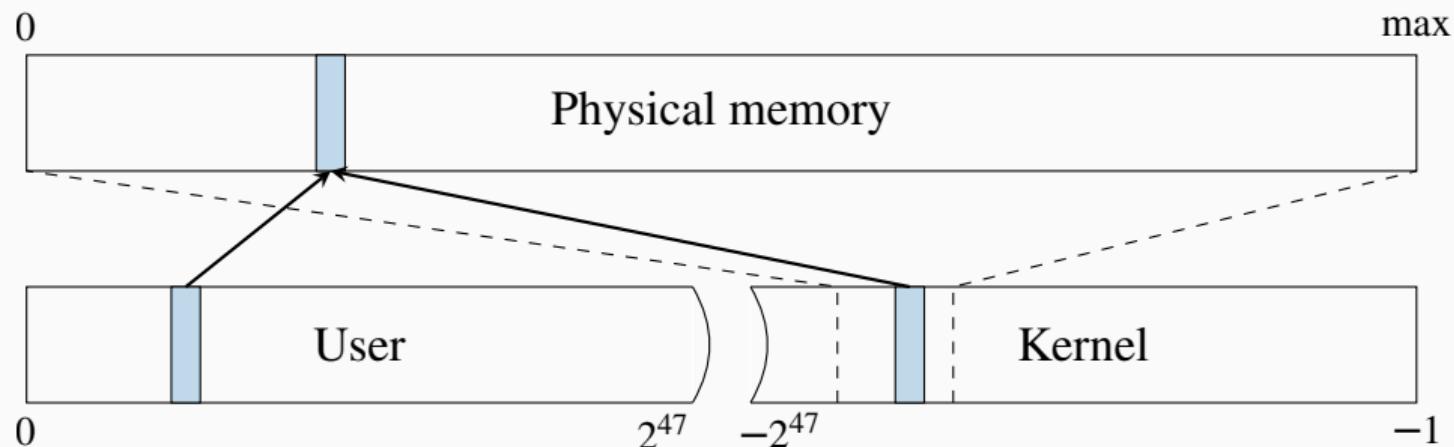

- **Mémoire virtuelle** : tous les accès mémoire faits par un processeur sont traduits en adresse physique

- Un processus ne peut donc pas lire/écrire une donnée d'un autre processus

- Mais tout le kernel est en général mappé dans l'espace virtuel du processus...

- ...et toute la mémoire physique est mappée dans le kernel

- En cas d'accès à une adresse virtuelle du kernel : exception

- Les vérifications des droits et l'accès lui-même sont faits en parallèle...

- Faire un accès en lecture à une adresse kernel qui provoque une exception

- Modifier l'état du cache en fonction du résultat de la valeur lue avec une instruction exécutée out-of-order

- Consulter l'état du cache pour savoir quelle valeur a été lue dans le kernel

```

; rcx = kernel address, rbx = probe_array

xor rax, rax

mov al, byte [rcx]

shl rax, 0xc

mov rbx, qword [rbx + rax]

```

- Faire en sorte que l'exception ne termine pas le programme

- Forker un processus fils avant de faire l'accès et lire le résultat dans le processus père

- Capturer le signal SIGINT

- Utiliser la mémoire transactionnelle

- Prefetch ⇒ Utiliser des pages différentes

- Lecture fréquente de la valeur 0

- Inclure une boucle de retry (exécutée spéculativement)

- Refaire l'attaque si la valeur 0x0 est lue

- Compromis taux d'erreur ⇔ Vitesse de lecture de la mémoire

- Permet de lire la mémoire kernel à une vitesse de 500 KB/s

- Avec un taux d'erreur de 0.003% (sur un Core i7)

- Attaque réussie sur tous les processeurs Intel testés, sur tous les OS

- Attaque réussie sur 1 seul processeur ARM, aucun AMD

- Des variantes de l'attaque possible sur ARM en utilisant une autre covert channel

- **Contre-mesures logicielles** :

- Ne pas mapper toute la mémoire physique dans le kernel (patch en cours de réalisation à l'époque pour une autre raison, dont Meltdown a accéléré l'intégration)

- **Contre-mesures matérielles** :

- Séquentialiser la vérification de permission dans la TLB et le load de la valeur

- Segmenter l'espace virtuel en deux : Kernel vs. user ⇒ Vérification triviale (cf. Mips)

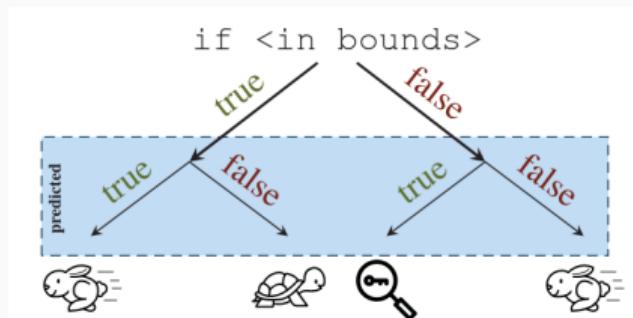

- Meltdown n'est que la première attaque d'une classe d'attaques appelées **attaques micro-architecturales** ; la 2e plus connue est **Spectre**

- Principe de l'attaque :

```

if (x < array1_size) {

y = array2[array1[x] * 4096];

}

```

- Exploite le prédicteur de branchement (source : article Spectre)

- Supposons que :

- $x$  est choisi de manière malicieuse (hors borne), et tel que  $array1[x]$  soit un octet secret  $k$  dans la mémoire du processus victime

- $array1\_size$  et  $array2$  sont non cachés, mais  $k$  est caché

- Les opérations précédentes ont reçues des valeurs de  $x$  valides, menant le prédicteur à supposer que le branchement va échouer.

- $\Rightarrow$  Fuite possible de l'octet secret  $k$

- Récemment, de nombreuses autres attaques exploitant des failles micro-architecturales

- **Foreshadow** [Van Bulck et al., 2018, Weisse et al., 2018] : variante de Meltdown, permet de lire des données à l'intérieur d'une enclave SGX

- **ZombieLoad** [Schwarz et al., 2019] : variante de Meltdown qui exploite un *Fill-Buffer*

- **RIDL** [van Schaik et al., 2019] : variante de Meltdown qui exploite des *Line-Fill buffers*

- **Fallout** [Canella et al., 2019] : variante de Meltdown qui exploite le *store buffer*

- Pour plusieurs de ces attaques, les vols de données peuvent se faire avec des hypothèses restreintes (ex : code javascript)

# Classification des attaques de type Meltdown et Spectre

- Classification sur le site <https://transient.fail> (TU Graaz)

- **Hertzbleed** [Wang et al., 2022] : exploite la variation de fréquence induite par le changement de consommation, permet de déduire des clés secrètes

- **IChannels** [Haj-Yahya et al., 2021] : exploite le temps pris par des instructions “couteuses” (SIMD) pour que la fréquence et le voltage s’adaptent, permet de faire des covert channels

- Attaques exploitant la température, etc.

# Merci !

Contact :

Email : [quentin.meunier@lip6.fr](mailto:quentin.meunier@lip6.fr)

-  Canella, C., Genkin, D., Giner, L., Gruss, D., Lipp, M., Minkin, M., Moghimi, D., Piessens, F., Schwarz, M., Sunar, B., Van Bulck, J., and Yarom, Y. (2019).

**Fallout : Leaking data on meltdown-resistant cpus.**

In Proceedings of the ACM SIGSAC Conference on Computer and Communications Security (CCS). ACM.

-  Gruss, D., Maurice, C., Wagner, K., and Mangard, S. (2016).

**Flush+ flush : a fast and stealthy cache attack.**

In International Conference on Detection of Intrusions and Malware, and Vulnerability Assessment, pages 279–299. Springer.

-  Gruss, D., Spreitzer, R., and Mangard, S. (2015).

**Cache template attacks : Automating attacks on inclusive last-level caches.**

In 24th {USENIX} Security Symposium ({USENIX} Security 15), pages 897–912.

-  Haj-Yahya, J., Orosa, L., Kim, J. S., Luna, J. G., Yağlıkçı, A. G., Alser, M., Puddu, I., and Mutlu, O. (2021).

**Ichannels : exploiting current management mechanisms to create covert channels in modern processors.**

In 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA), pages 985–998. IEEE.

-  Kocher, P., Horn, J., Fogh, A., Genkin, D., Gruss, D., Haas, W., Hamburg, M., Lipp, M., Mangard, S., Prescher, T., et al. (2020).

**Spectre attacks : Exploiting speculative execution.**

Communications of the ACM, 63(7) :93–101.

-  Lipp, M., Schwarz, M., Gruss, D., Prescher, T., Haas, W., Fogh, A., Horn, J., Mangard, S., Kocher, P., Genkin, D., Yarom, Y., and Hamburg, M. (2018).

**Meltdown : Reading kernel memory from user space.**

In 27th USENIX Security Symposium (USENIX Security 18).

-  Maurice, C., Weber, M., Schwarz, M., Giner, L., Gruss, D., Boano, C. A., Mangard, S., and Römer, K. (2017).

**Hello from the other side : Ssh over robust cache covert channels in the cloud.**

In NDSS, volume 17, pages 8–11.

-  Osvik, D. A., Shamir, A., and Tromer, E. (2006).

**Cache attacks and countermeasures : the case of aes.**

In Cryptographers' track at the RSA conference, pages 1–20. Springer.

-  Schwarz, M., Lipp, M., Moghimi, D., Van Bulck, J., Stecklina, J., Prescher, T., and Gruss, D. (2019).

**ZombieLoad : Cross-privilege-boundary data sampling.**

In CCS.

-  Van Bulck, J., Minkin, M., Weisse, O., Genkin, D., Kasikci, B., Piessens, F., Silberstein, M., Wenisch, T. F., Yarom, Y., and Strackx, R. (2018).

**Foreshadow : Extracting the keys to the Intel SGX kingdom with transient out-of-order execution.**

In Proceedings of the 27th USENIX Security Symposium. USENIX Association.

See also technical report Foreshadow-NG [Weisse et al., 2018].

-  van Schaik, S., Milburn, A., Österlund, S., Frigo, P., Maisuradze, G., Razavi, K., Bos, H., and Giuffrida, C. (2019).

**RIDL : Rogue in-flight data load.**

In S&P.

-  Wang, Y., Paccagnella, R., He, E. T., Shacham, H., Fletcher, C. W., and Kohlbrenner, D. (2022).

**Hertzbleed : Turning power {Side-Channel} attacks into remote timing attacks on x86.**

In 31st USENIX Security Symposium (USENIX Security 22), pages 679–697.

-  Weisse, O., Van Bulck, J., Minkin, M., Genkin, D., Kasikci, B., Piessens, F., Silberstein, M., Strackx, R., Wenisch, T. F., and Yarom, Y. (2018).

**Foreshadow-NG : Breaking the virtual memory abstraction with transient out-of-order execution.**

Technical report.

See also USENIX Security paper Foreshadow [Van Bulck et al., 2018].

-  Yarom, Y. and Falkner, K. (2014).

**Flush+ reload : a high resolution, low noise, L3 cache side-channel attack.**

In 23rd USENIX Security Symposium (USENIX) Security 14, pages 719–732.